- ●图片

- 视频●

主要指标:

l VPX 6U版型

l 2片TMS320C6678

l 4片XC7K410T

l 支持2路千兆以太网

l 支持PCIe/SRIO

主要指标:

l VPX 6U版型

l 2片TMS320C6678

l 4片XC7K410T

l 支持2路千兆以太网

l 支持PCIe/SRIO

主要指标:

l VPX 6U版型

l 2片TMS320C6678

l 4片XC7K410T

l 支持2路千兆以太网

l 支持PCIe/SRIO

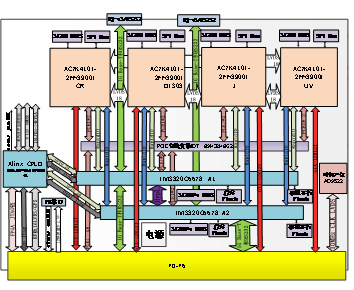

框图:

产品:

产品简介

1. 从P0供电,(主板提供输出+12V(40A),+5V(25),-12V(1 A),3.3V(15A))。

2. GTX和PCIE最高速度6.25Gbps。

3. DDR3选用MT41J512M8-125,一个FPGA一片DDR3(512MB),一个DSP四片DDR3(2GB)。

4. Fpga的Rom选用可以x4的串行加载,DSP和FPGA的JTAG拉到CPLD,且在板子上放一个FPGA和DSP的JTAG插座。

5. 两个DSP和CPLD之间互连24个IO和JTAG。

6. CPLD作为系统的启动控制,所有的四个FPGA串行加载线和JTAG都连到CPLD,可是实现DSP动态加载4片FPGA(采用JTAG或者串行rom),也可以由4个SPIrom分别加载。动态加载问题方式需要确认。

7. CPLD负责系统电源控制和启动配置,来出8个LED指示灯和8个跳线,CPLD与每个FPGA包含4对LVDS。

8. RF板过来的16对LVDS和2对GPS的LVDS连接到CPLD。

9. 系统时钟基准采用背板提供的10MHz LVDS信号,时钟芯片也可以不采用AD9522。

10. DSP采用TMS320C6678,串行FLASH用于存储系统数据,TMS320C6678#1是主DSP,连接千兆网口和RS232,千兆网口可能需要PHY芯片和变压器,每个DSP都往前面板放置一个网口和RS232,另外一个网口和RS232拉到底板。

11. 两片DSP放置两片FLASH存储数据。

12. FPGA选用XC7K410T-2FFG900I,FPGA之间连接18对LVDS(2对GCLK,16对Data)形成环行链。

13. PA接口包括4路RS485差分对输出和12路0-2.5V的模拟量输入,4路RS485输出分别由4个FPGA(每个FPGA 1路)通过485驱动实现,12路0-2.5V的模拟量分别连接到4个FPGA(每个FPGA连接3路模拟量)的ADC采样输入IO。

14. 2片DSP、4片FPGA、背板(PCEIx8)的PCEI分别连接到PCIE*2交换芯片IDT89H24。

15. 2片DSP之间采用HyperLink连接。

16. 4片FPGA的2个GTX分别连接到每片DSP RapidIO 。

17. 4片FPGA分别连接12对GTX到底板。

18. P0-P6的管脚定义附后。

19. FPGA的PCIE和Rapidio在同一个bank。

20. GTX的一个bank上的两个参考钟都加上,(待讨论:其中PCIE 100MHz, Rapidio 125MHz, GTX 250MHz)。

21. 做系统启动控制

主要技术支持:

l DSP开发支持(引导程序、TCP/IP网络通信程序、SRIO与FPGA通信程序)

l FPGA程序支持(SRIO程序,时钟控制程序)

l 三个月技术服务