PXIe高精度多功能调制信号源

1、概述

拟设计一款高精度多功能调制信号源,该调制源支持模拟调制和数字调制。

2、设计指标要求

• 通道数:2(可以同时输出IQ信号或者两路IF信号)

• 输出阻抗:50欧姆

• 输出耦合方式:DC耦合

• 输出最大幅值:1Vpp

• 模拟调制功能:

AM

模拟调制频率范围:DC~20Mhz

调幅深度:0 ~ 100%

调幅失真:30%时小于1.5%

FM

模拟调制频率范围:DC~20Mhz

调制频偏范围:<20Mhz

贫频偏失真:1.5%

PM

调制频率范围:DC~20Mhz

相偏范围:0°~360°

调相失真:<1%

6 ) 数字调制功能:

调制格式:BPSK、QPSK、8PSK、16QAM、32QAM、64QAM、128QAM、256QAM、MSK、GMSK、2FSK

滤波器类型:升余弦滤波器(RCOSFIR)、平方根升余弦滤波器(RRCOSFIR)、高斯滤波器(GAUSSFIR)

滤波器滚降系数:0~1

符号速率:DC~4M

EVM:<3%rms(符号速率4M,平方根升余弦滤波器,滚降系数为0.5,QPSK调制)

基带信号过采样率:>400倍

基带信号播放速率:1600MSPS

基带信号带宽:<50M

采样位宽:16bit

IF信号:DC~400Mhz

IF信号频率稳定度:1PPM

IF相位噪声:120dBC/Hz@10khz,125Mhz(单频)

外时钟频率:10Mhz

外时钟输入功率:-10dbm~10dbm

3、实现原理

1)、综述

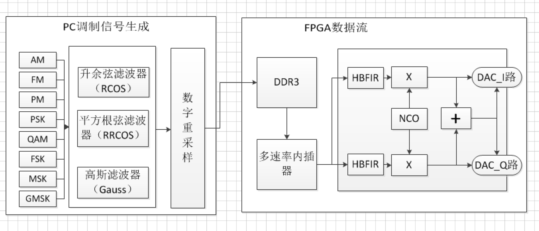

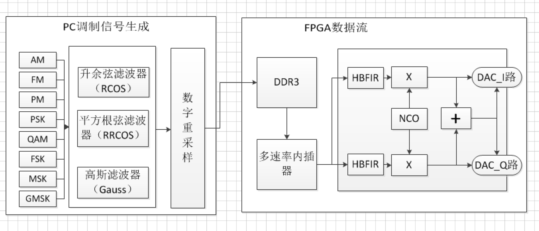

基带信号定义:信源(信息源,也称发送端)发出的没有经过调制(进行频谱搬移和变换)的原始电信号,其特点是频率较低,信号频谱从零频附近开始,具有低通形式。根据原始电信号的特征,基带信号可分为数字基带信号和模拟基带信号(相应地,信源也分为数字信源和模拟信源。)其由信源决定。而数字基带和模拟基带又分很多中调制方式,常见的数字调制方式有下面几大类有:PSK、QAM、FSK、MSK、GMSK、ASK等。常见的模拟调制有下面几大类:AM、FM、PM等。要在FPGA中实现这么多的调制方式是非常复杂的,在PC中实现这些调制就相对容易。基带信号要插值到同DAC相同的采样率,运算量大,正好可以利用FPGA实时性好,可以并行处理的特点,在FPGA做插值运算。所以此模块基于PC+FPGA的方式来实现,PC实现各种调制算法,FPGA负责插值到DAC的采样率。

2)、原理描述

首先PC通过算法来产生随机序列的二进制比特流,二进制比特流经过不通的调制算法来映射成响应的IQ调制信号。由于调制后的IQ数据流信号不适合在在信道中传输,即要通过成型滤波器整形成适合在信道中传输的信号(此处模拟信号默认不使用成型滤波器)。成型滤波器包括如下三种:

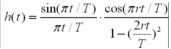

升余弦滚降滤波器其时域冲击响应为:

公式(1)

r为滚降系数(r=0时即为理想低通滤波器brickwall filter,现实中不可实现。),T为输入符号的符号周期。

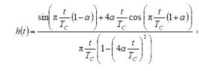

平方根升余弦滚降滤波器其时域冲击响应为:

公式(2)

α为滚降系数,T为输入符号的符号周期。

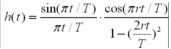

高斯滤波器其时域冲击响应为:

公式(3)

此时调制的信号经过数字重采样到统一的采样速率,便于FPGA中做信号处理。经过数字重采样后的信号通过PXI总线下发到FPGA上的DDR3中缓存,DDR3中的数据流经过多速率内插器内插到DAC的采样频率。接着由DAC芯片做进一步的插值到更高的采样率,同时DAC芯片可以产生正交的载波信号,此载波信号由DAC中的DDS产生,所以其正交性好。此时IQ基带信号可以和正交的载波信号混频后两路合成一路实信号输出,或直接输出IQ基带信号。实现框图如图1所示。

4、具体指标分析

略

5、关键器件

采用FPGA+DA架构,FPGA采用Xilinx XC7K70T,DA采用ADI公司的AD9142A。

6、模块功耗及尺寸

模块功耗为12瓦;尺寸为标准3