2GSPS手持采集记录仪

一、概述

为了实现宽带信号便携式采集,拟开发一款1通道采集仪,该采集仪带2GSPS单采集通道,同时可以实现信号存储、分析、显示。

二、主要参数

l 采集通道:1通道

l 通道1频率:2GSPS@12bit

l 显示屏:7寸

l 架构方式:Arm+FPGA

l FPGA: Xilinx K7 325T

l Arm: ZynQ xc7z020

l 系统:Win7

l 软件:VC

l 存储容量:2TB

l 存储速度:4GB/S

l 尺寸:200mm*125mm*65mm

l 重量:2.5Kg

三、框图

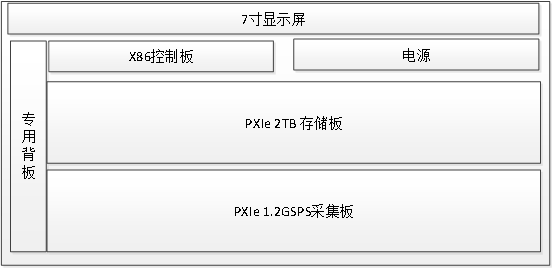

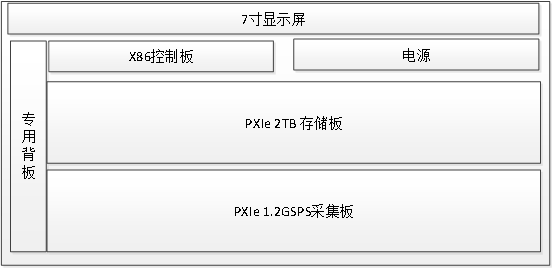

系统框图

效果图

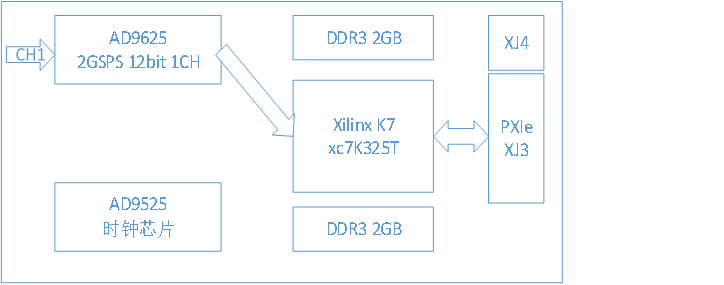

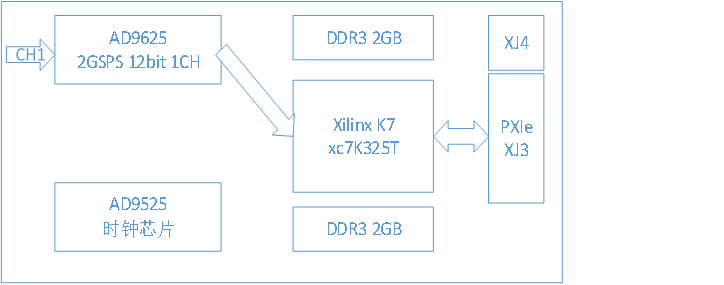

采集板卡框图

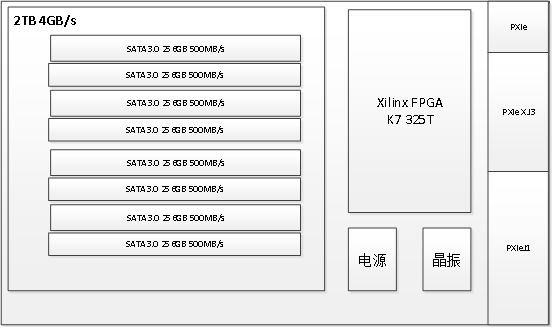

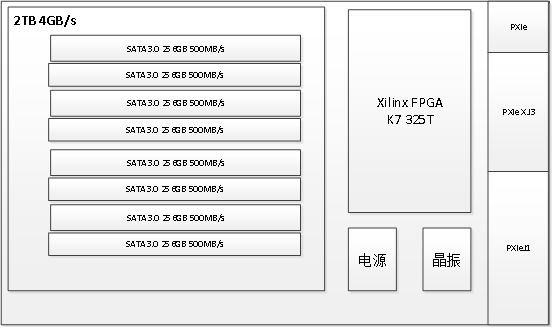

存储板卡框图

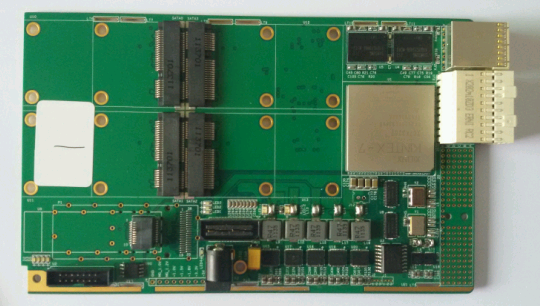

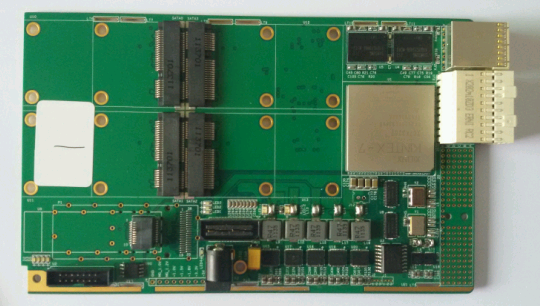

实物图:

四、设备描述

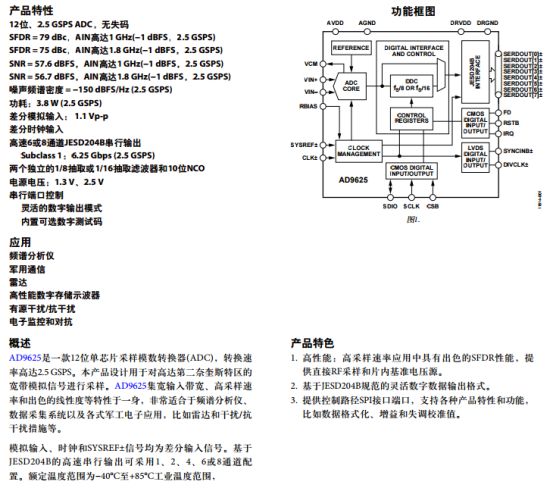

4.1 ADC1选型:

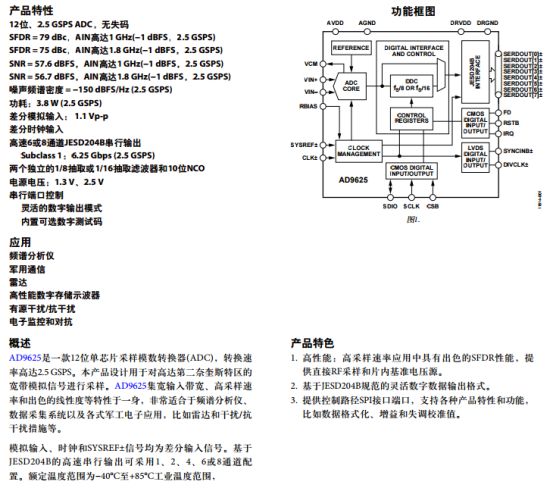

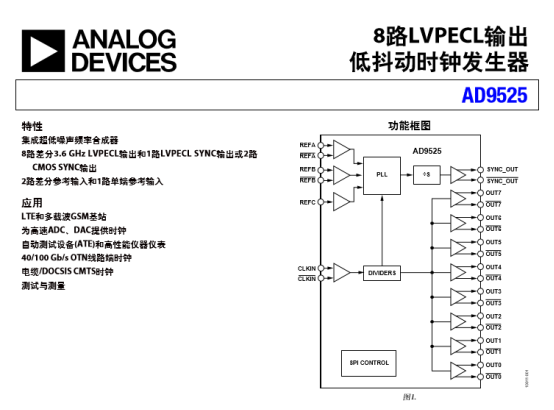

AD9625是一款采样率为2GSPS的ADC器件,但是该器件的一个新的版本可以获得更高的采样率。AD9625-2.5可以简化RF信号到数字信号的接口要求,它的内部集成了2个数字下变频器(DDC),两个数控振荡器(NCO)和一个为输出数据提供串行连接的可配置的JESD204B。

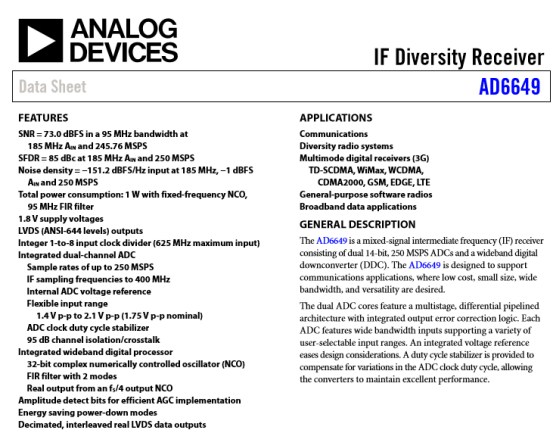

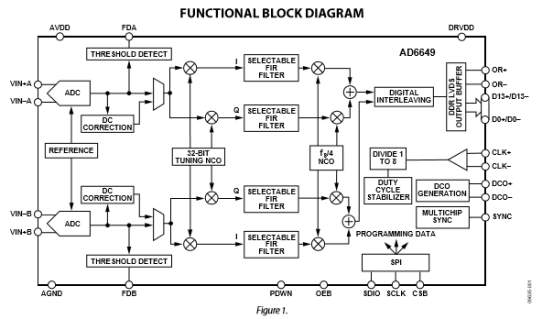

4.2 ADC2选型

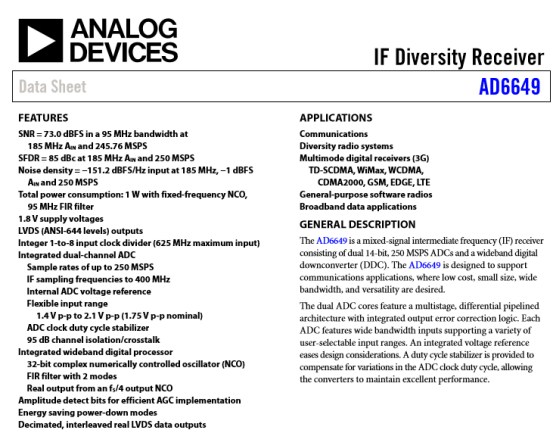

AD6649是一款可以工作在140MSPS的双通道ADC ,本项目使用1片实现1通道140MSPS采集,1通道70MSPS采集。

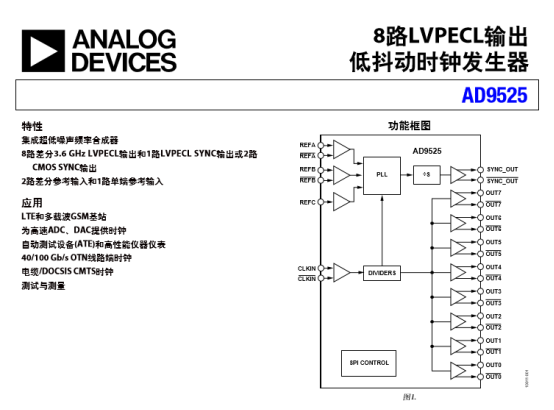

4.3 时钟芯片选型:

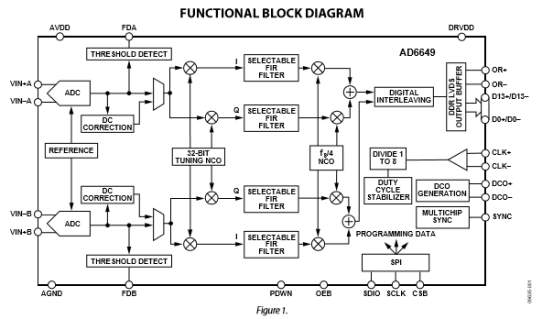

本设计拟采用AD9525作为时钟芯片。

4.4 FPGA控制

FPGA采用Xilinx K7 325T,该芯片Kintex™-7 325T 现场可编程门阵列(FPGA), 成为业界推出最快的28nm新一代可编程逻辑器件产品。Kintex-7 FPGA 将以最低的功耗提供最优的性价比,以满足主要应用需求。与此同时,Kintex-7 FPGA 系列产品利用28nm 7系列所共享的统一架构,还可以支持客户也能马上着手那些最终将迁移至Artix™-7 和 Virtex®-7 FPGA的设计。K7功耗明显比V6低很多。Kintex-7 器件将同赛灵思 ISE® 13 设计套件、AMBA® 4 高级可扩展接口 (AXI™)总线协议兼容 IP 和目标参考设计一并提供,所有这些目标设计平台的组件都将在此次演示的全新Kintex-7 FPGA KC705 评估板上运行。设计人员可以对全新Kintex-7 K325T器件的功耗、性能和功能进行全面评估。依靠台积电(TSMC)公司建立在业经验证的设计和制造方法之上的 28nm 高性能、低功耗(HPL)工艺。下面是芯片内部资料。

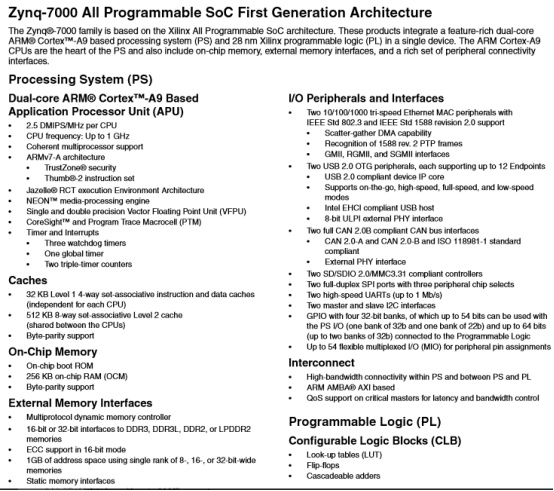

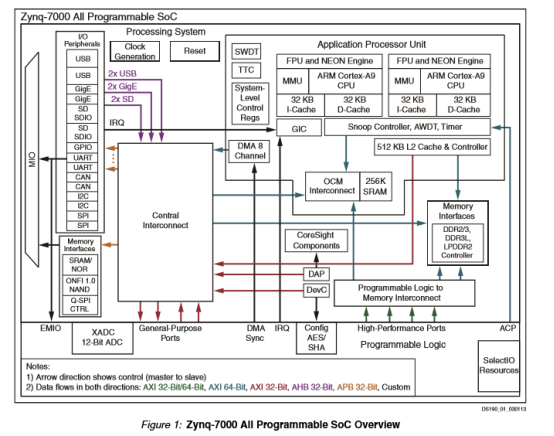

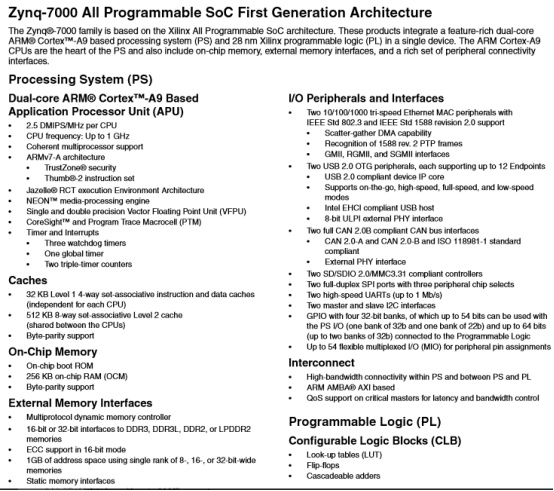

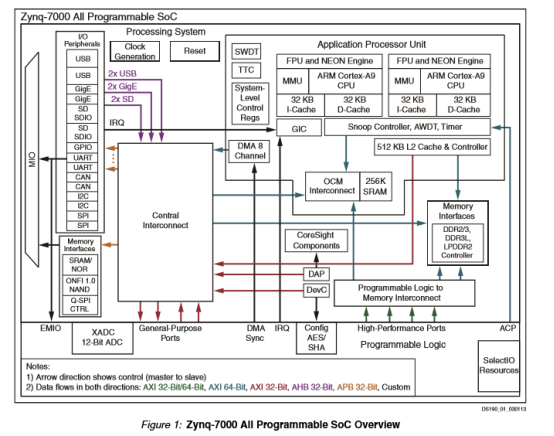

4.5 Arm控制

Arm采用Zynq,Zynq基于ARM 双核CortexA9 的应用处理器,ARM-v7架构,高达1GHz,单/双精度浮点单元,NEON多媒体处理引擎;

缓存

每个CPU 32KB 1级指令和数据缓存,512KB 2级缓存,2个CPU共享,支持8位奇偶校验;

片内存储

片上boot ROM,256KB 片内RAM

外部存储接口

多协议动态内存控制器,16/32 bit DDR2、DDR3接口,16位ECC支持,1GB地址空间,静态存储接口: 8bit SRAM,并行NOR Flash,ONFI1.0 NANDFlash接口,1-4bit SPI Flash支持

IO外设和接口

两个千兆网卡支持:发散-聚集DMA ,GMII,RGMII,SGMII接口

两个USB2.0 OTG接口,每个最多支持12节点

两个CAN2.0B总线接口

两个SD卡、SDIO、MMC兼容控制器

2个SPI,2个UARTs,2个I2C接口

4组32bit GPIO,54(32+22)作为PS系统IO,64连接到PL

互联

PS内和PS到PL的高带宽连接

基于ARM AMBA AXI总线

传输质量控制和带宽控制

可编程逻辑(PL)概述

可编程逻辑块

LUT、触发器、级联加法器

36Kb 块RAM

全双口

最高72bit宽度

可编程IO块

支持LVCMOS,LVDS和SSTL

1.2V到3.3V IO

可编程延时和SerDes

Zynq-7020特定的性能和资源量

PS:CPU有800MHz

PL:85K逻辑单元(约等效于130万门);53.2K 查找表;106K触发器;220个DSP单元;2个12bit XADC最多17通道

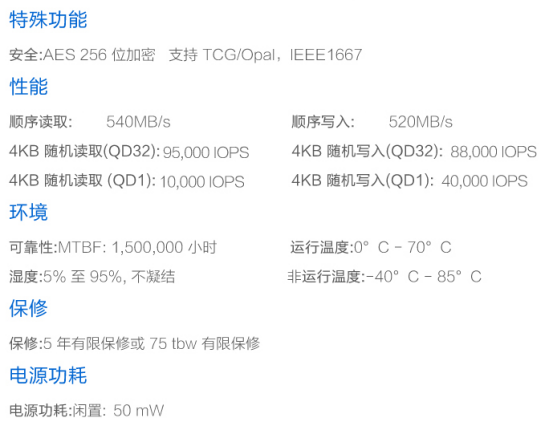

4.6存储部分

存储实现是利用FPGA驱动8路SATA固态盘实现的,每路固态盘速率可达到500MB/s,从而组合实现一个4GB/s读写速度的固态盘。

下面是固态盘的资料: